|

| Compensated 10ns analog delay element | Folded transmission line delay on high Er material BW 200-600MHz

Piggyback RFIC based gain blocks for loss compensation and gain leveling 1997 for Elisra Micro-Electronics |

| Custom wide band discriminator 200-1200MHz | Feasibility study and preliminary design using Maxim's Quick-Chip technology

1997 for Elisra Micro-Electronics |

| Custom log-IF stage 600-2400MHz | Feasibility study, discrete design and preliminary die design using Maxim's Quick-Chip technology

1998 for Elisra Micro-Electronics |

| GPS receiver for integration into cellphone front-end | Feasibility study and technology selection

IP design, evaluation board and documentation 2000 for CellGuide Ltd. |

| T/R WLAN chipset definition | Feasibility study and technology selection

Development and risk reduction plan  2001 for CommPrize Ltd. |

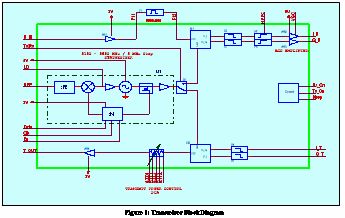

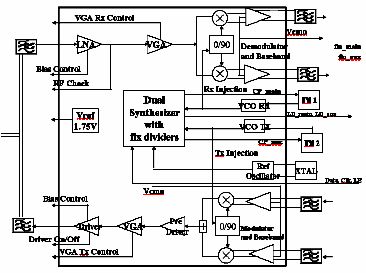

| Cable based high data rate data communication duplex user module | Planned prototyping and production using IBM's 6-layer SiGe process

System optimization for RFIC implementation Identification of compatible IP and cost analysis SMT Packaging simulation and determination of critical isolation requirements  2002 for Tiaris Ltd. |

| Novel Device test structure | Support for the design of a special device test fixture

Implementation using Intel's 0.13um process with special customization  2006 for Intel Jerusalem Ltd. |